Xilinx社の FPGA の開発環境である Vivado MLを使用して、Kria KV260のPMODの1pinに出力するKria KV260のFPGAのプログラムを作成します。Digilent社製のJtagデバイス「JTAG HS-3」を使用してFPGAへの書き込み、Kria KV260のPMODの1pinの出力をオシロスコープ「ISDS205A」で確認します。

ここでは、「Vivado MLによるKria KV260のFPGAのプログラム作成(その1)」の継続作業となります。

Kria KV260とJtagデバイス「JTAG HS-3」との接続

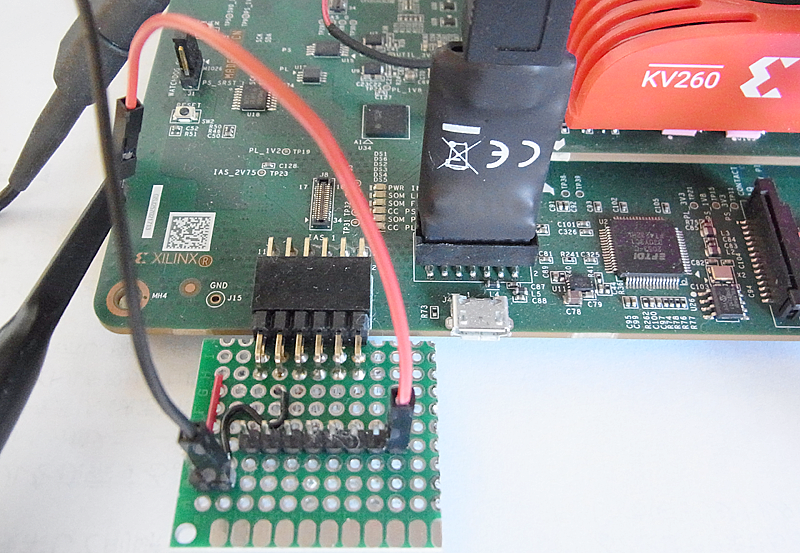

Jtagデバイス「JTAG HS-3」とKria KV260のPMODの信号を引き出す自作の「PMOD拡張ボード」を次の画像のように接続します。「PMOD拡張ボード」にはオシロスコープ「ISDS205A」を接続します。

JTAG HS-3

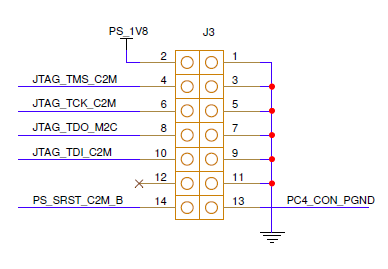

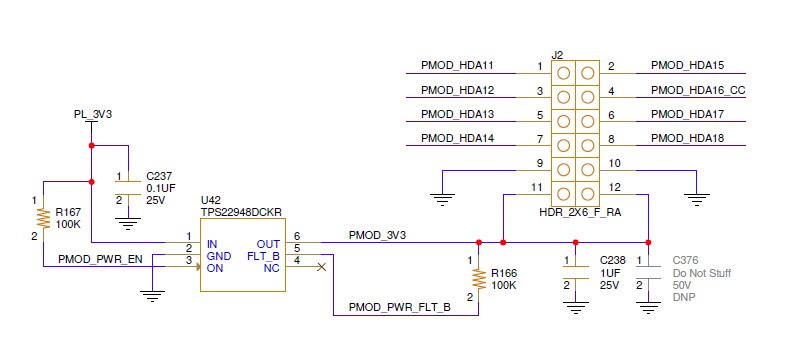

Kria KV260 starter kitのJtagコネクタの回路図を次に示します。

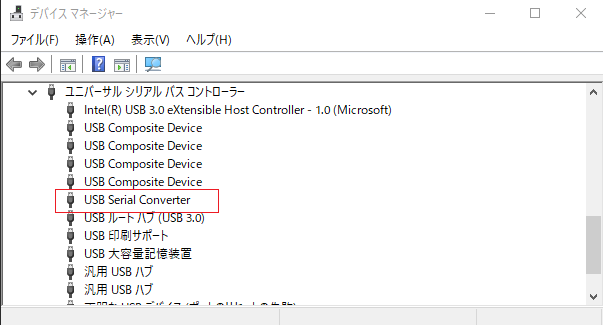

PCにJtagデバイス「JTAG HS-3」を接続し、デバイスマネージャーにより「USB Serial Converter」が次のように表示されることを確認します。

Jtagデバイス「JTAG HS-3」ドライバを次の手順でインストールします。

- Jtagデバイス「JTAG HS-3」のケーブルを取り外します。

- CD コマンドでディレクトリを 「<ザイリンクスのインストール ディレクトリ>\digilent」(H:\Xilinx\Vivado\2021.2\data\xicom\cable_drivers\nt64\digilent) に変更します。

- 「install_digilent.exe 」を管理者権限で実行し、インストールのウィザードを完了します。

- Jtagデバイス「JTAG HS-3」のケーブルを再度接続します。

PMOD拡張ボード

Kria KV260 starter kitのPMODコネクタの回路図を次に示します。

PMOD拡張ボードは、PMODコネクタから信号を外部に取り出すために自作したボードで、8ビットの信号、電源、グランドを取り出せます。オシロスコープ「ISDS205A」は「PMOD拡張ボード」の1pinとグランドに接続します。

Kria KV260のPMODのxdcファイル作成

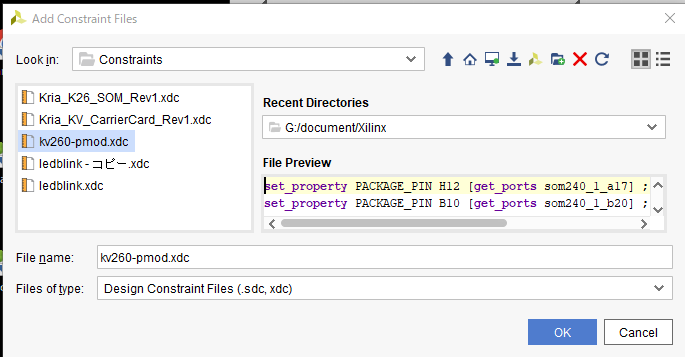

Kria KV260のPMODのxdcファイル作成を次のように作成し、「G:\document\Xilinx\Constraints」に保存します。

kv260-pmod.xdc

set_property PACKAGE_PIN H12 [get_ports som240_1_a17] ;# PMOD pin 1 - som240_1_a17 set_property PACKAGE_PIN B10 [get_ports som240_1_b20] ;# PMOD pin 2 - som240_1_b20 set_property PACKAGE_PIN E10 [get_ports som240_1_d20] ;# PMOD pin 3 - som240_1_d20 set_property PACKAGE_PIN E12 [get_ports som240_1_b21] ;# PMOD pin 4 - som240_1_b21 set_property PACKAGE_PIN D10 [get_ports som240_1_d21] ;# PMOD pin 5 - som240_1_d21 set_property PACKAGE_PIN D11 [get_ports som240_1_b22] ;# PMOD pin 6 - som240_1_b22 set_property PACKAGE_PIN C11 [get_ports som240_1_d22] ;# PMOD pin 7 - som240_1_d22 set_property PACKAGE_PIN B11 [get_ports som240_1_c22] ;# PMOD pin 8 - som240_1_c22 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_a17"]; # Net name HDA11 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_d20"]; # Net name HDA12 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_d21"]; # Net name HDA13 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_d22"]; # Net name HDA14 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_b20"]; # Net name HDA15 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_b21"]; # Net name HDA16_CC set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_b22"]; # Net name HDA17 set_property IOSTANDARD LVCMOS33 [get_ports "som240_1_c22"]; # Net name HDA18 set_property SLEW SLOW [get_ports "som240_1_a17"]; # Net name HDA11 set_property SLEW SLOW [get_ports "som240_1_d20"]; # Net name HDA12 set_property SLEW SLOW [get_ports "som240_1_d21"]; # Net name HDA13 set_property SLEW SLOW [get_ports "som240_1_d22"]; # Net name HDA14 set_property SLEW SLOW [get_ports "som240_1_b20"]; # Net name HDA15 set_property SLEW SLOW [get_ports "som240_1_b21"]; # Net name HDA16_CC set_property SLEW SLOW [get_ports "som240_1_b22"]; # Net name HDA17 set_property SLEW SLOW [get_ports "som240_1_c22"]; # Net name HDA18 set_property DRIVE 4 [get_ports "som240_1_a17"]; # Net name HDA11 set_property DRIVE 4 [get_ports "som240_1_d20"]; # Net name HDA12 set_property DRIVE 4 [get_ports "som240_1_d21"]; # Net name HDA13 set_property DRIVE 4 [get_ports "som240_1_d22"]; # Net name HDA14 set_property DRIVE 4 [get_ports "som240_1_b20"]; # Net name HDA15 set_property DRIVE 4 [get_ports "som240_1_b21"]; # Net name HDA16_CC set_property DRIVE 4 [get_ports "som240_1_b22"]; # Net name HDA17 set_property DRIVE 4 [get_ports "som240_1_c22"]; # Net name HDA18

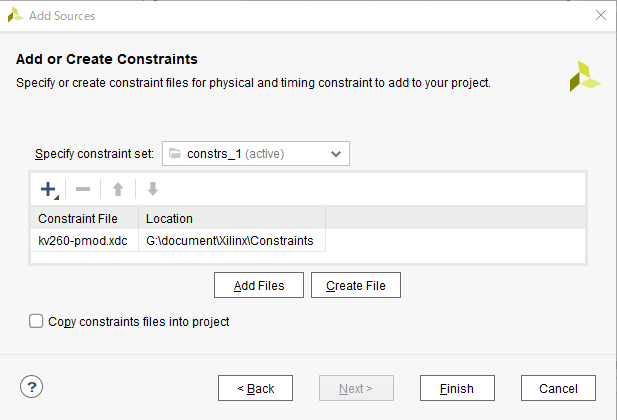

次の手順で作成したPMODのxdcファイル「kv260-pmod.xdc」を登録します。

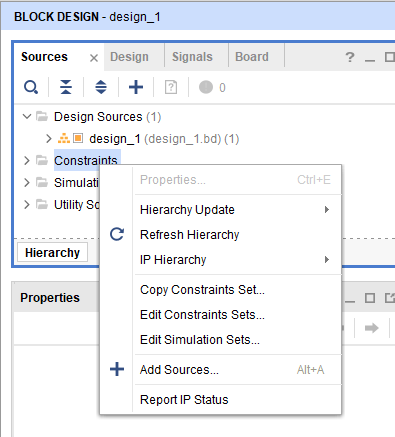

- 「Constraints」上で右クリックして、表示されたメニューから「Add Sources」をクリックします。

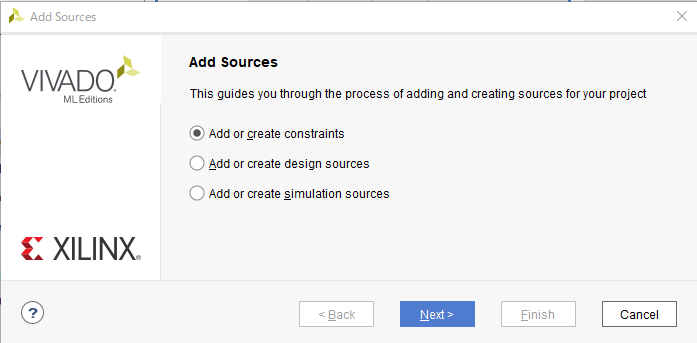

- 表示された画面で「Add or create contraints」を選択して「NEXT」ボタンをクリックします。

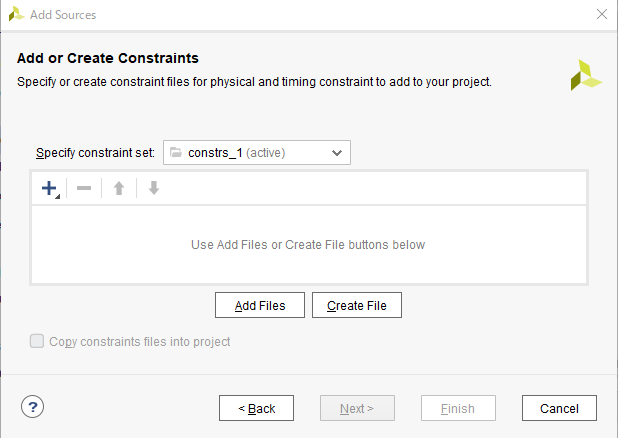

- 表示された画面で「Add Files」ボタンをクリックします。

- 「…\Xilinx\Constraints」フォルダの下に作成したxdcファイル「kv260-pmod.xdc」を選択し、「OK」ボタンをクリックします。

- 「Add or Create Constraints」画面が表示され、「Finish」ボタンをクリックします。

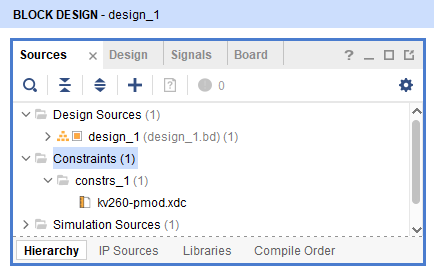

- 「Sources」タブを選択し、「Constraints」をクリックすると作成されたxdcファイルが表示されます。

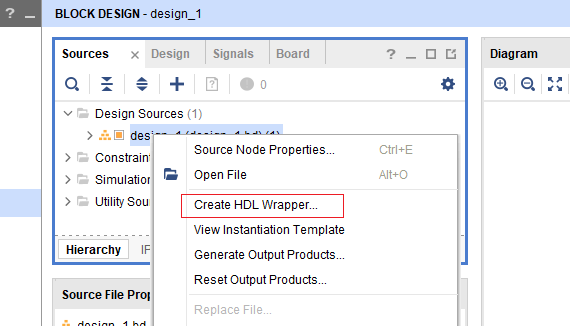

最上位HDLラッパーの作成

blinkモジュールが最上位となっているため、Zynqとblinkの両方を含む最上位モジュールを作成します。

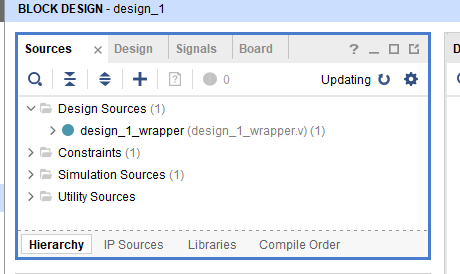

「Design Sources」の「design_1」を右クリックして表示したメニューから、「Create HDL Wrapper」をクリックします。

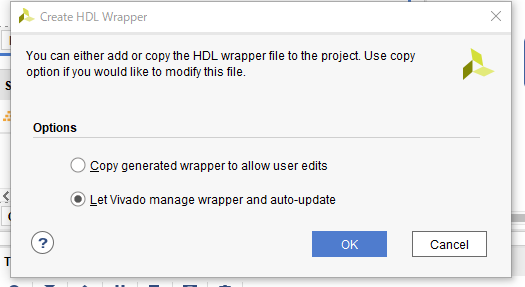

そのまま「OK」ボタンをクリックします。

階層「design_1_wrapper」が作成されます。

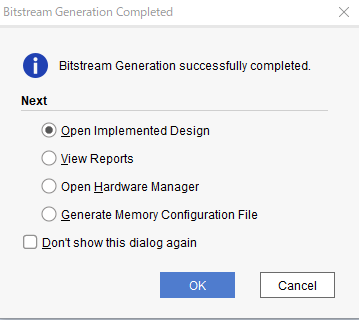

ビットストリームファイルの生成

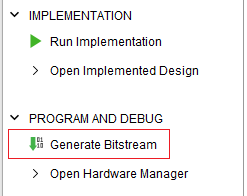

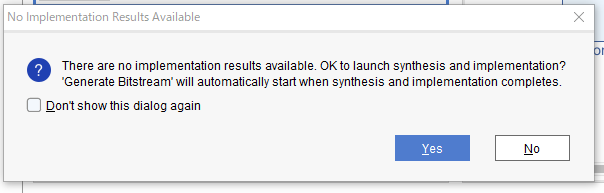

左端の「Flow Navigator」より「PROGRAM AND DEBUG」の「Generate Bitstream」をクリックし、コンフィグファイルの作成を実施します。

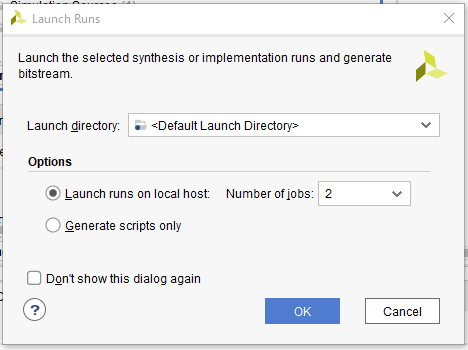

「OK」ボタンを押します。

「OK」ボタンを押します。

「Cancel」ボタンを押します。

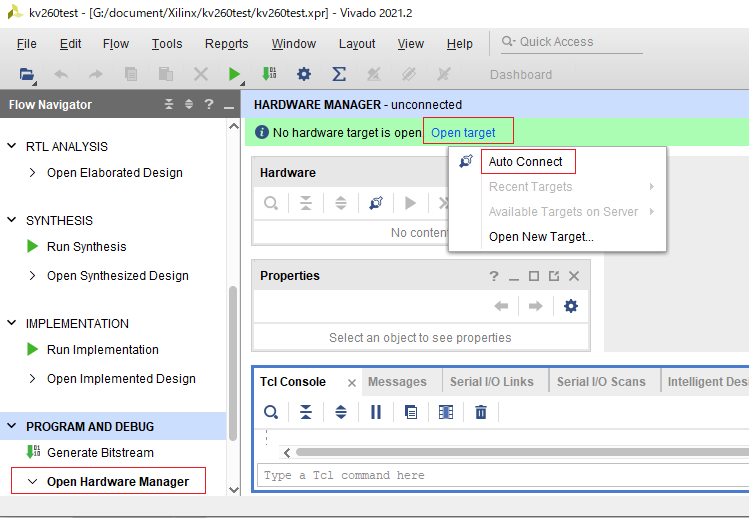

FPGAへの書き込み

Jtagデバイス「JTAG HS-3」を使って、Kria KV260のFPGAに書き込みます。現在原因は調査中ですが、処理途中で2度キャンセルしてエラーダイアログが表示されました。

- 左端の「Flow Navigator」より「PROGRAM AND DEBUG」の「Open Hardware Manager」をクリックし、上側の「Open Target」をクリックして「Auto Connect」を選択します。

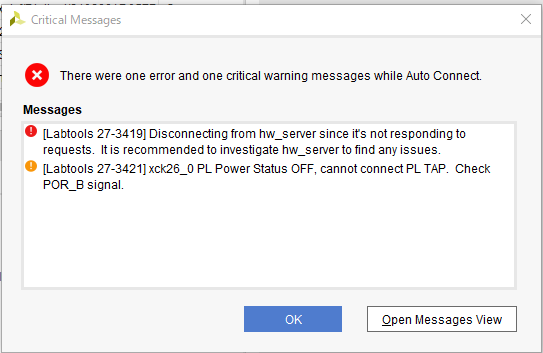

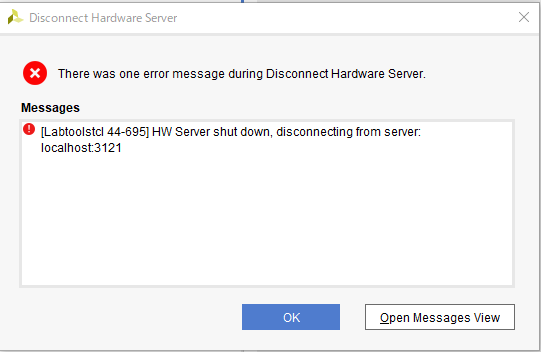

- 接続に時間がかかりすぎるので「Cancel」ボタンを押すと、次のエラー画面が表示されました。「OK」ボタンを押します。

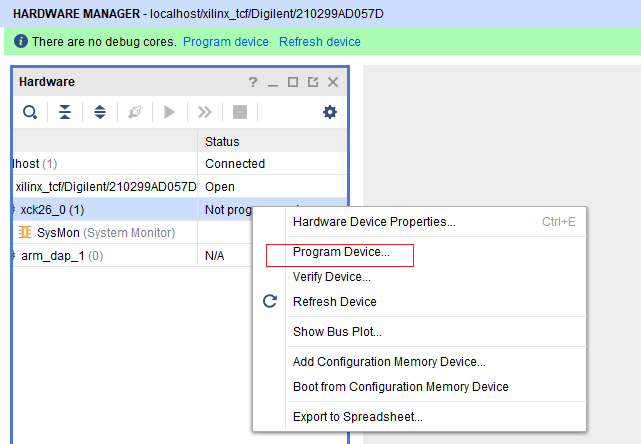

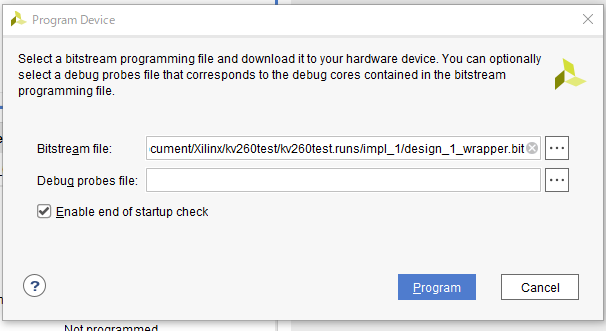

- 「Not program」を選択して右クリックし、表示されたメニューで「Program Device」を選択します。

- 画面が表示されビットストリームファイルの選択となるため、そのまま「Program」ボタンをクリックします。

- 書き込みが終了しないので「Cancel」ボタンを押すと、次のエラー画面が表示されました。「OK」ボタンを押します。

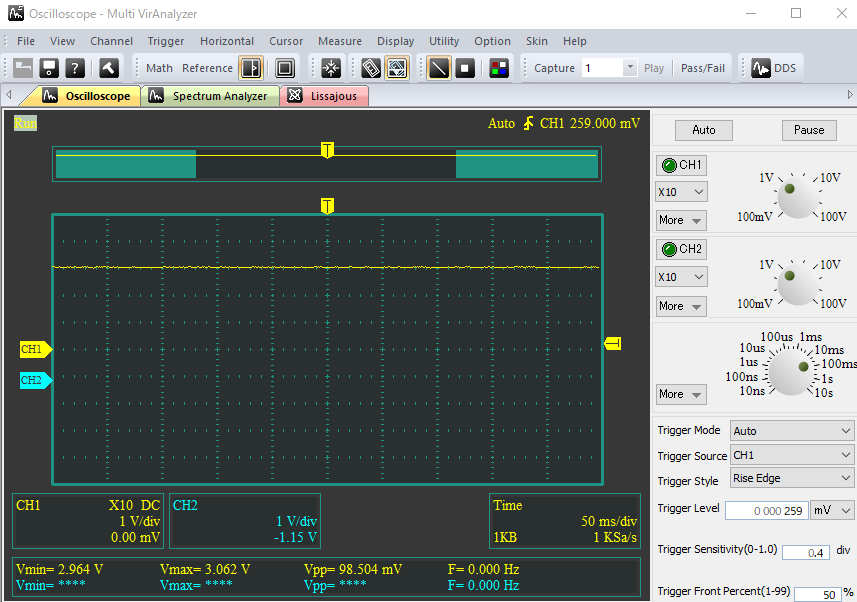

- オシロスコープ「ISDS205A」で確認すると「PMOD拡張ボード」の1pinに3.062Vの電圧が発生しました。

エラー解析のためにTcl Consoleのログを取得しました。

Scanning sources...

Finished scanning sources

INFO: [IP_Flow 19-234] Refreshing IP repositories

INFO: [IP_Flow 19-1704] No user IP repositories specified

INFO: [IP_Flow 19-2313] Loaded Vivado IP repository 'H:/Xilinx/Vivado/2021.2/data/ip'.

open_project: Time (s): cpu = 00:00:19 ; elapsed = 00:00:11 . Memory (MB): peak = 1590.977 ; gain = 0.000

update_compile_order -fileset sources_1

open_bd_design {G:/document/Xilinx/kv260test/kv260test.srcs/sources_1/bd/design_1/design_1.bd}

Reading block design file <G:/document/Xilinx/kv260test/kv260test.srcs/sources_1/bd/design_1/design_1.bd>...

Adding component instance block -- xilinx.com:ip:xlconstant:1.1 - xlconstant_0

Successfully read diagram <design_1> from block design file <G:/document/Xilinx/kv260test/kv260test.srcs/sources_1/bd/design_1/design_1.bd>

open_bd_design: Time (s): cpu = 00:00:09 ; elapsed = 00:00:08 . Memory (MB): peak = 1590.977 ; gain = 0.000

open_hw_manager

connect_hw_server -allow_non_jtag

INFO: [Labtools 27-2285] Connecting to hw_server url TCP:localhost:3121

INFO: [Labtools 27-3415] Connecting to cs_server url TCP:localhost:3042

INFO: [Labtools 27-3417] Launching cs_server...

INFO: [Labtools 27-2221] Launch Output:

******** Xilinx cs_server v2021.2.0

****** Build date : Sep 28 2021-06:44:20

**** Build number : 2021.2.1632779060

** Copyright 2017-2022 Xilinx, Inc. All Rights Reserved.

connect_hw_server: Time (s): cpu = 00:00:19 ; elapsed = 00:06:51 . Memory (MB): peak = 1590.977 ; gain = 0.000

open_hw_target

INFO: [Labtoolstcl 44-466] Opening hw_target localhost:3121/xilinx_tcf/Digilent/210299AD057D

INFO: [Common 17-41] Interrupt caught. Command should exit soon.

ERROR: [Labtools 27-3419] Disconnecting from hw_server since it's not responding to requests. It is recommended to investigate hw_server to find any issues.

CRITICAL WARNING: [Labtools 27-3421] xck26_0 PL Power Status OFF, cannot connect PL TAP. Check POR_B signal.

open_hw_target: Time (s): cpu = 00:00:28 ; elapsed = 00:09:32 . Memory (MB): peak = 2945.672 ; gain = 1354.695

INFO: [Common 17-344] 'open_hw_target' was cancelled

set_property PROBES.FILE {} [get_hw_devices xck26_0]

set_property FULL_PROBES.FILE {} [get_hw_devices xck26_0]

set_property PROGRAM.FILE {G:/document/Xilinx/kv260test/kv260test.runs/impl_1/design_1_wrapper.bit} [get_hw_devices xck26_0]

program_hw_devices [get_hw_devices xck26_0]

INFO: [Labtools 27-3164] End of startup status: HIGH

program_hw_devices: Time (s): cpu = 00:00:06 ; elapsed = 00:01:06 . Memory (MB): peak = 3003.562 ; gain = 5.871

refresh_hw_device [lindex [get_hw_devices xck26_0] 0]

INFO: [Common 17-41] Interrupt caught. Command should exit soon.

ERROR: [Labtools 27-3419] Disconnecting from hw_server since it's not responding to requests. It is recommended to investigate hw_server to find any issues.

INFO: [Labtools 27-1434] Device xck26 (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it.

INFO: [Common 17-344] 'refresh_hw_device' was cancelled

ERROR: [Labtoolstcl 44-695] HW Server shut down, disconnecting from server: localhost:3121

ERROR: [Labtools 27-3419] Disconnecting from hw_server since it’s not responding to requests. It is recommended to investigate hw_server to find any issues.

次のような回答を見つけました。Windows特有の問題らしく、Linuxでは発生しないということでした。

And just to confirm: this is a problem with the Windows version. The Linux version of the hardware server has no such problem.