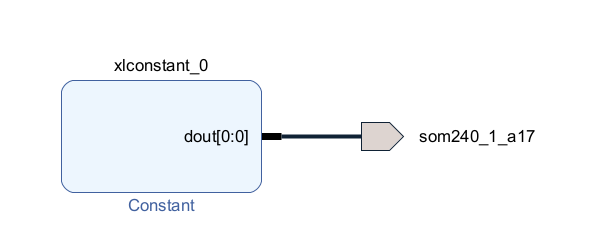

Xilinx社の FPGA の開発環境である Vivado MLを使用して、Kria KV260のPMODの1pinに出力するKria KV260のFPGAのプログラムを作成します。FPGAへの書き込みにはDigilent社製のJtagデバイス「JTAG HS-3」を使用します。ここでの手順ではIP「Constant」を使って、Kria KV260のPMODの1pinに出力する次のブロックデザインを作成します。

作成作業の続きは「Vivado MLによるKria KV260のFPGAのプログラム作成(その2)」に示します。

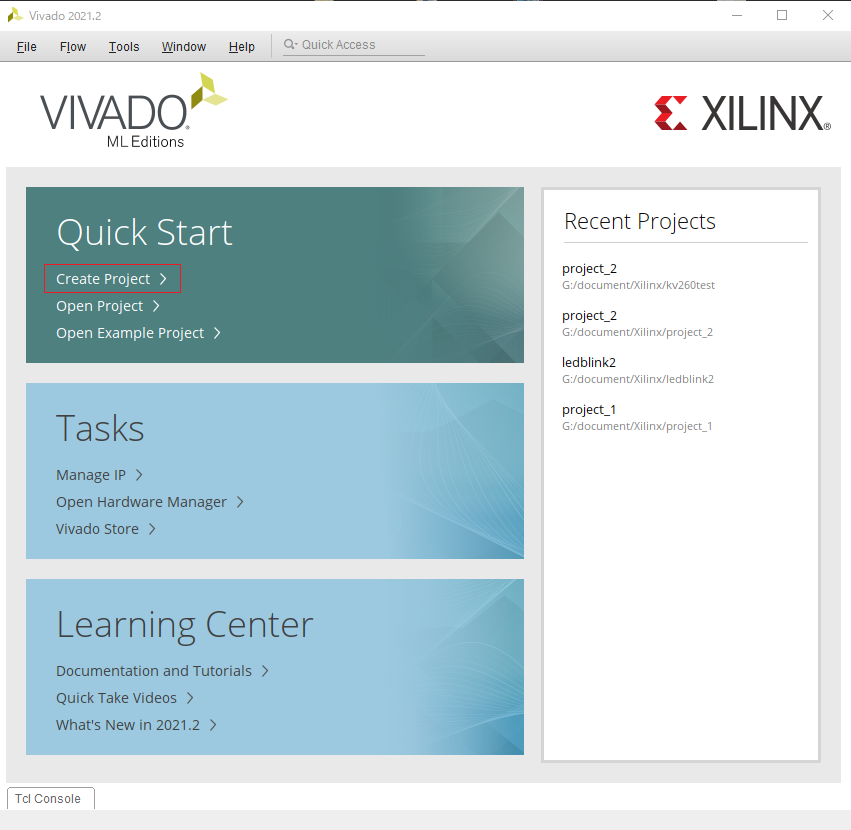

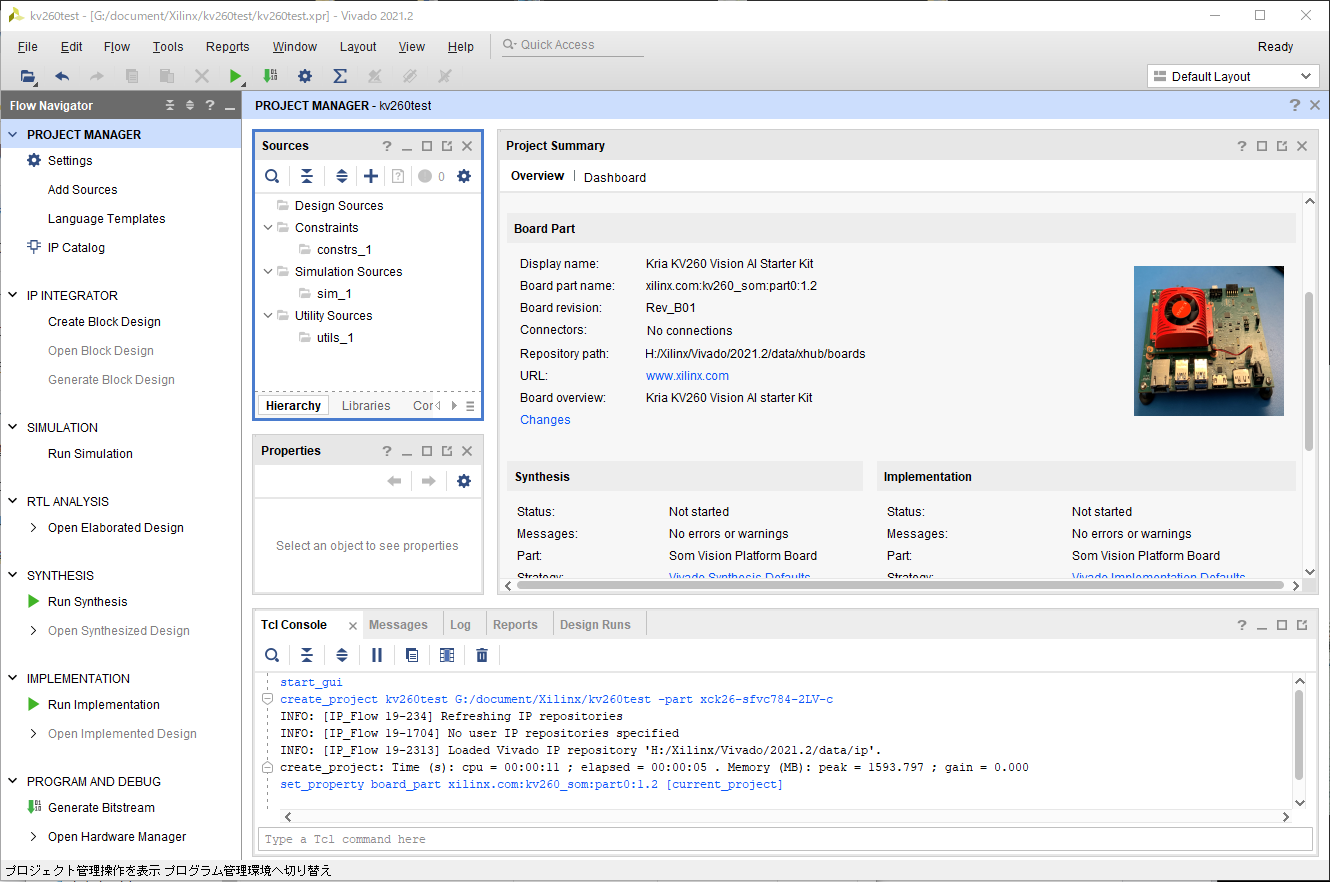

プロジェクト作成

- 「Quick Start」から「Create Project」をクリックします。

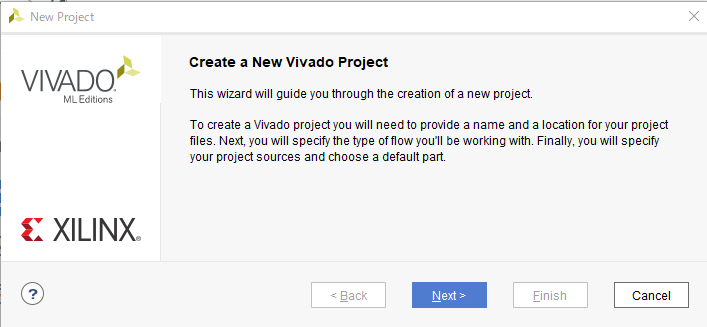

- 「Next」ボタンをクリックします。

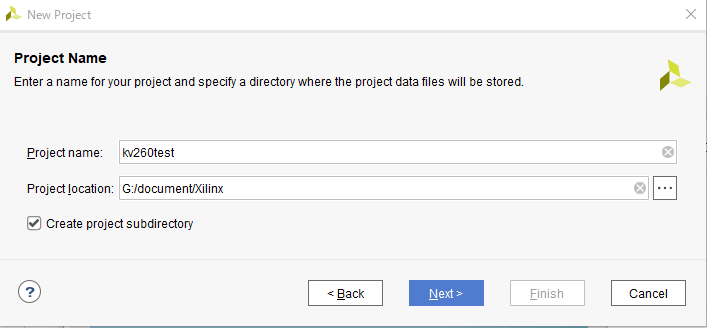

- Project name「Project name」と「Project location」を設定して「Next」ボタンをクリックします。

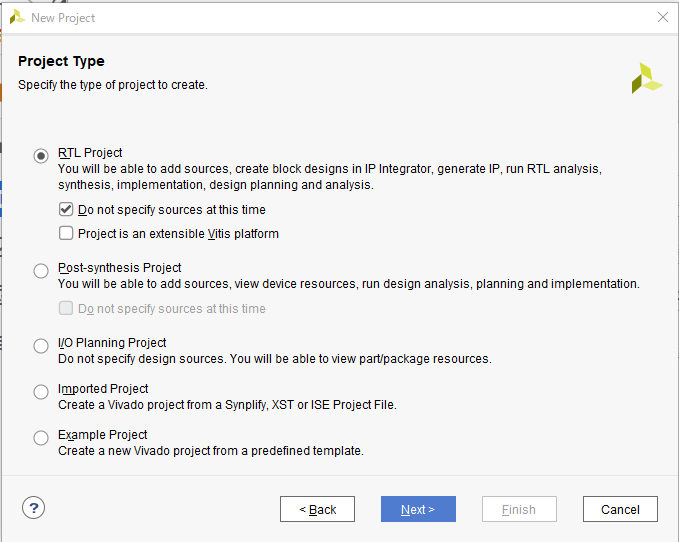

- 「Next」ボタンをクリックします。

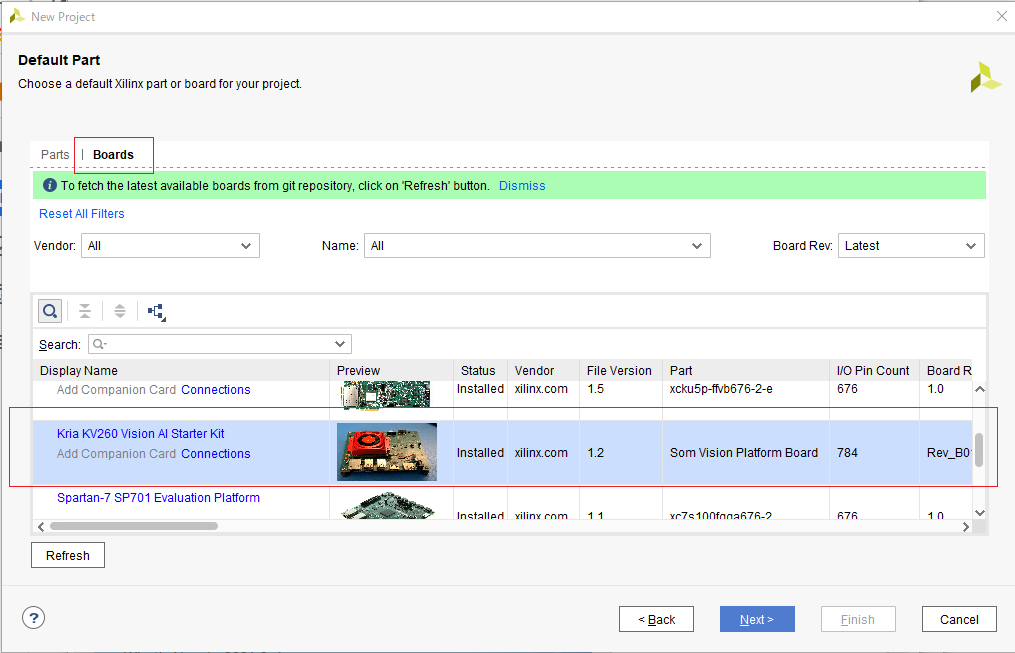

- 「Boards」タブをクリックし、「Kria KV260 starter kit」を選択し、「Next」ボタンをクリックします。

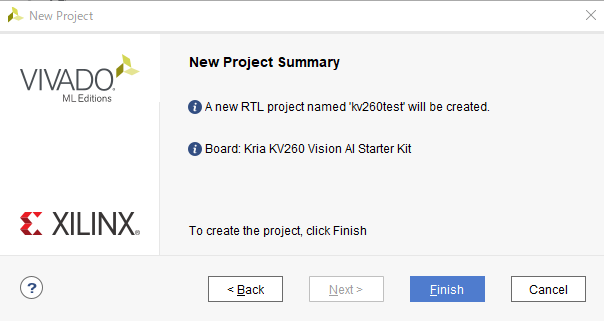

- 確認画面が表示されるので「Finish」ボタンをクリックします。

- 次のようにプロジェクトが作成されます。

RTL(レジスタ転送レベル)プログラミングとは、レジスタと組み合わせ回路の機能を記述するプログラミング手法です。主にFPGAデバイスを動作させるために、論理回路をハードウェア記述言語(HDL)で設計・記述します。

ブロックデザイン

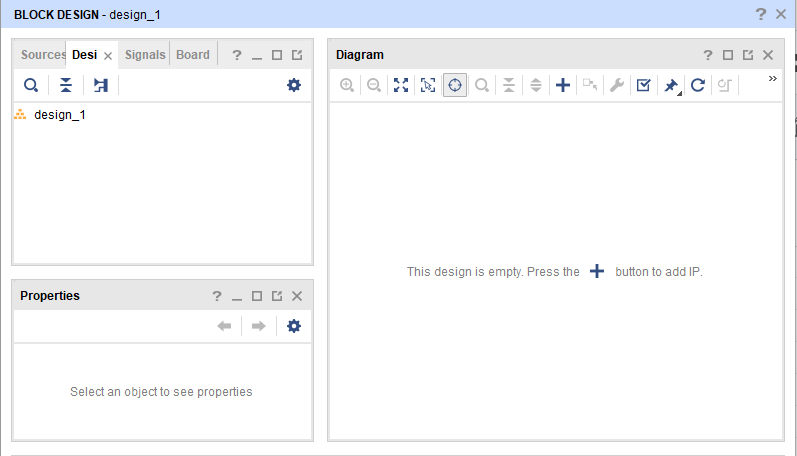

- 左端の「Flow Navigator」より「IP INTEGRATOR」の「Create Block Design」をクリックします。ダイアログが表示されるので、そのまま「OK」ボタンを押します。

- ブロックデザインの画面が表示されます

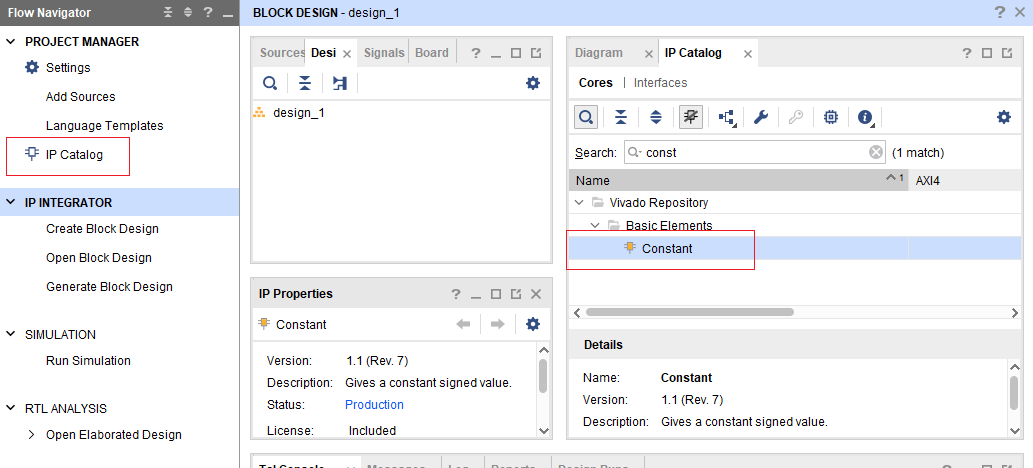

- 左端の「Flow Navigator」より「Project 」の「IP Catalog」をクリックします。検索欄に「const」を設定し、「Constant」を選択してダブルクリックします。

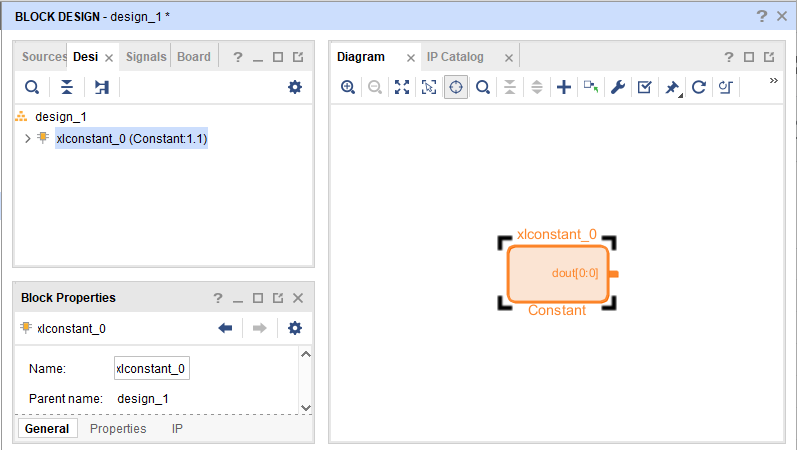

- 画面にIP「Constant」が表示されます。

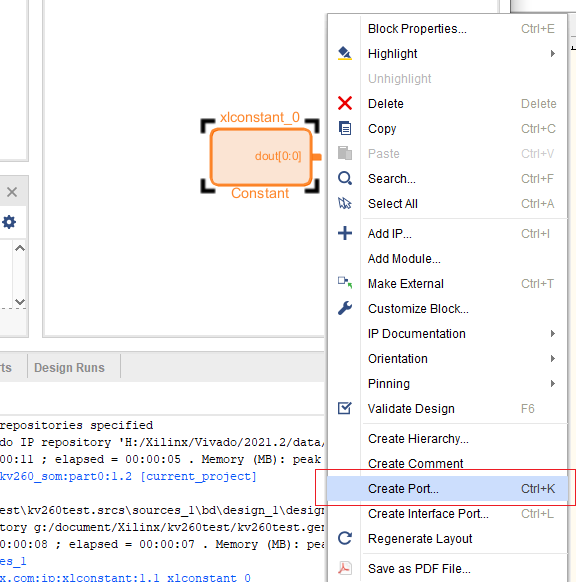

- 画面上で右クリックして、表示されたメニューから「Create Port」を選択します。

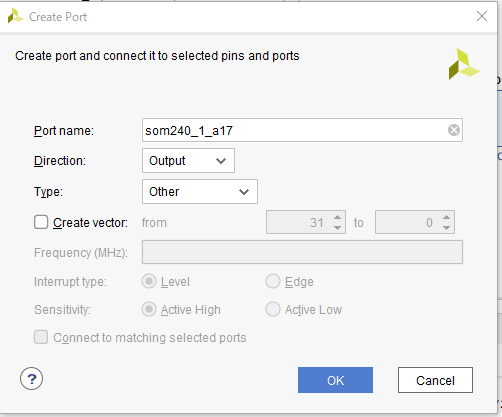

- 表示されたダイアログで次のように設定し、「OK」ボタンを押します。

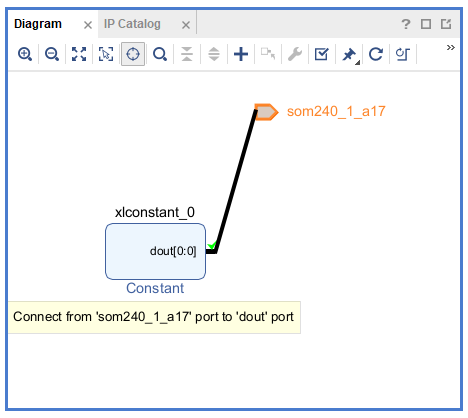

- IP「Constant」の端子「dout」を作成したPort「som240_1_a17」に接続します。

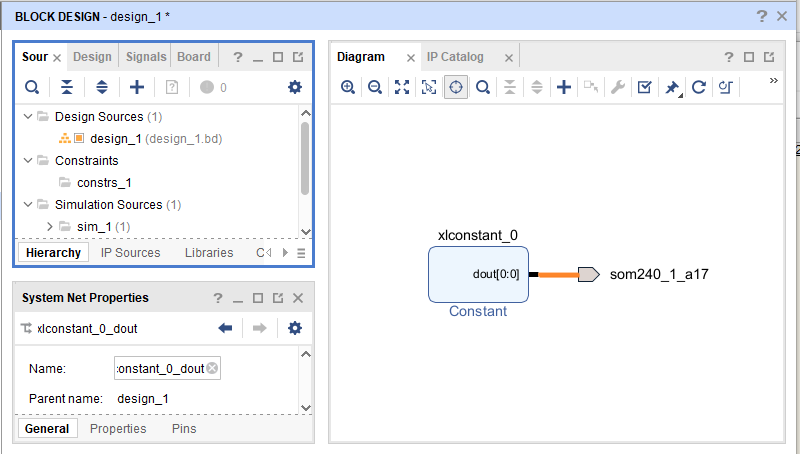

- 接続のレイアウトを再描画すると次のように表示されます。