KV260でLEDチカを行います。「KV260でLEDチカ(その2)」へ続きます。

Vivado でプロジェクト作成

「Vivado MLによるKria KV260のFPGAのプログラム作成(その1)」に従ってプロジェクトを作成します。プロジェクト名は「LEDTest」とします。

Block Designer を利用してクロックを作成

KV260 は PL(Programmable Logic)に繋がる外部端子にクロックはありません。しかしクロックに同期して動くロジックを記述するRTLプログラミングではまずクロックが必要です。このため、PS(Processor System)からクロックを貰う必要があります。「KV260でSystemVerilogでLEDチカしてみる」を参考に作業を行います。

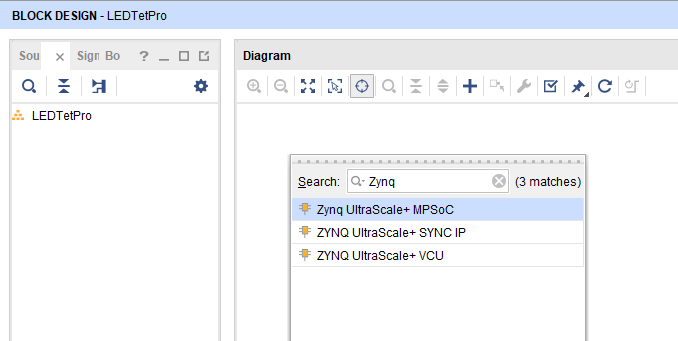

- 「Create Block Design 」を選択して、Design name「LEDTetPro」を作成します。

- 開いたダイアログの+ ボタンを押して、「Zynq UltraScale MPSoC」 を選びます。

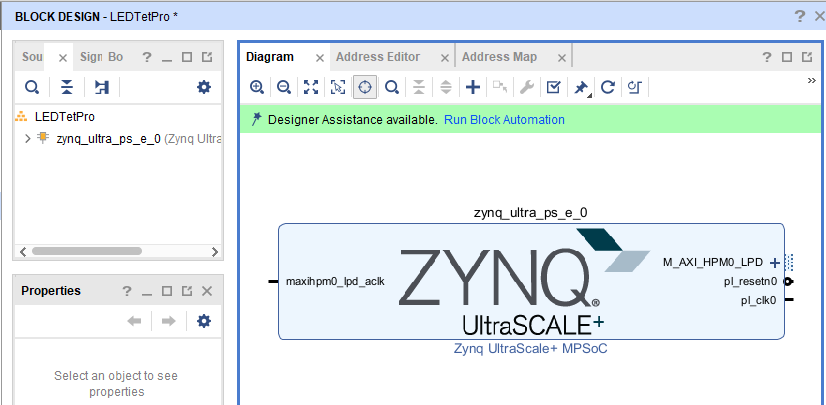

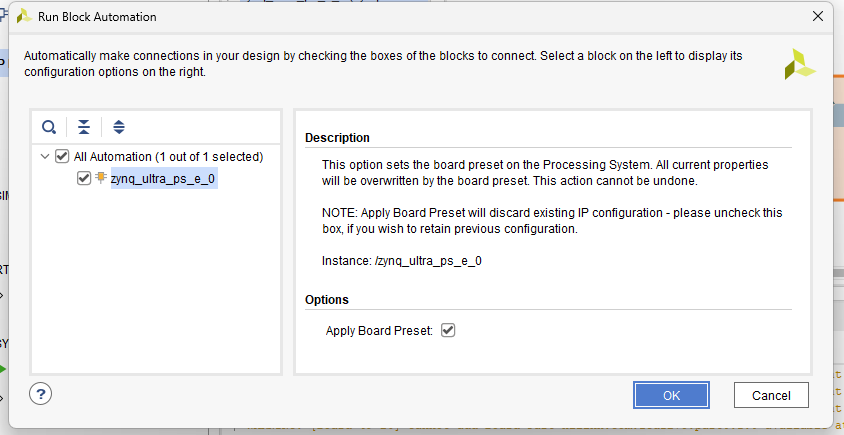

- 「Run Block Automation」を選択します。

- 「 Apply Board Preset 」にチェックが入っていることを確認します。

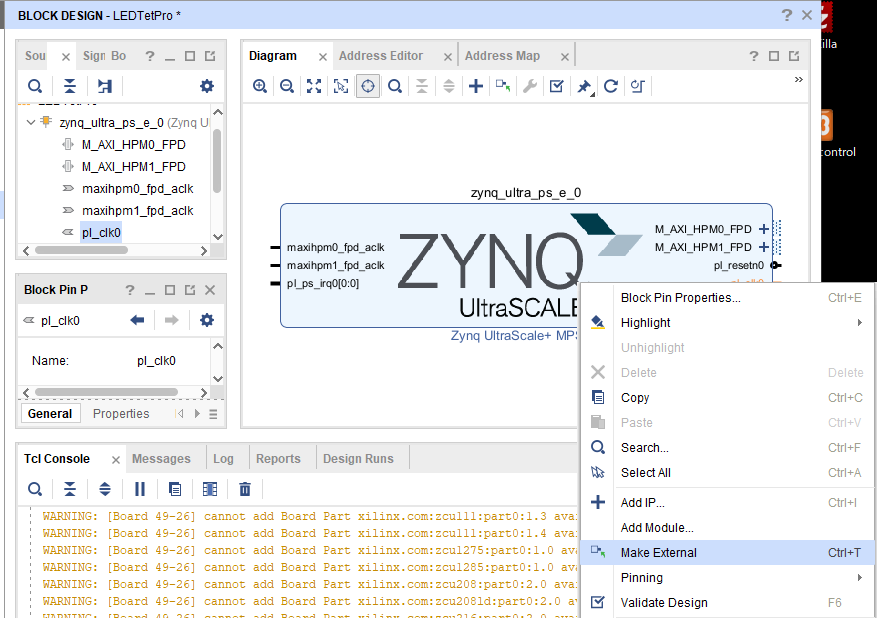

- クロック「pl_clk0 」を右クリックして 「Make External」を選択します。

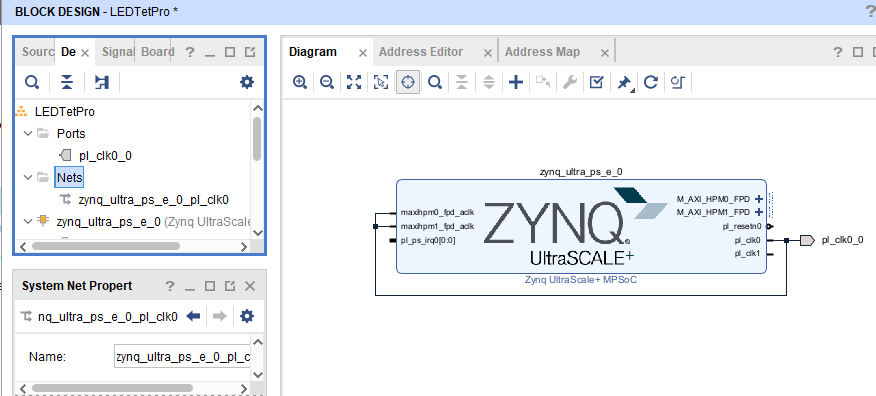

- Block Design の外に信号「pl-clk0_0」が引き出されます。「maxihpm0_aclk」 と 「maxihpm1_aclk 」にクロックが供給されていないのでエラーが出るため、クロックを接続します。

SystemVerilog でプログラムの記述

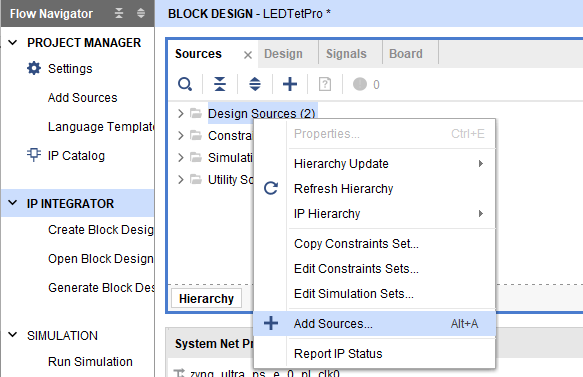

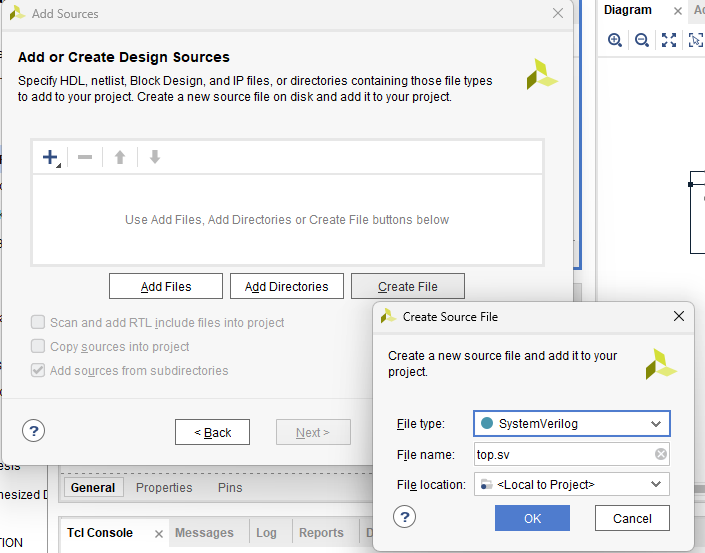

- Sources タブに切り替え、「Design Source」を右クリックして 「Add Source…」 を選択し、ソースコードを新規作成します

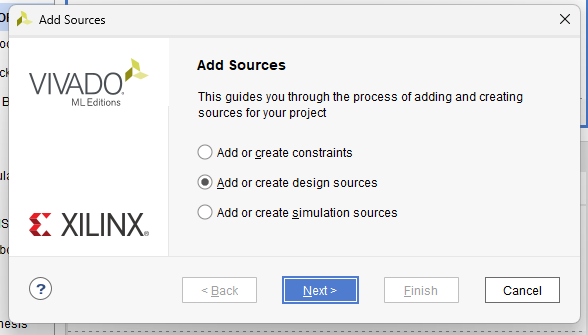

- 表示されたダイアログの「Add or create design source」にチェックを付けて 「Next 」を押します。

- 今回は新規に作成するので 「Create File」を押し、新規作成するソースコードの種類「SystemVerilog」とファイル名「top.sv 」を指定します。

- 表示されたダイアログの「Finsh 」を押します。

- 表示されたソースコードの初期状態のポート宣言するダイアログでは、「OK 」を押します。

- 新規のソースコードテンプレートが表示されるので、次のソースコード「top.sv」を書き込みます。

- 27-28行目で、引き出した信号「pl-clk0_0」を「clk」として定義します。

- moduleの信号接続で、ポート名、ネット名で接続する場合は次のように記述します。

module_name instance_name ( .portname(netname) );

top.sv

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2025/02/22 17:34:24 // Design Name: // Module Name: top // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module top( output var logic [0:0] led // LED用に出力を 1bit 定義 ); // ブロックデザインからクロックを引き出す logic clk; LEDTestPro i_design1(.pl_clk0_0(clk)); // クロックで動作する26bitのカウンタを作成 logic [25:0] counter = 0; always_ff @(posedge clk) begin counter <= counter + 1; end // カウンタの25bit目をLEDに出力 assign led = counter[25]; endmodule