Xilinx社の FPGA の開発環境であるVivado MLが持つシミュレーション機能を確認するために、Kria KV260のFPGAのプログラムを作成します。

作成作業の続きは、「Vivado MLによるプログラムシミュレーション-シミュレーションの実行」に示します。

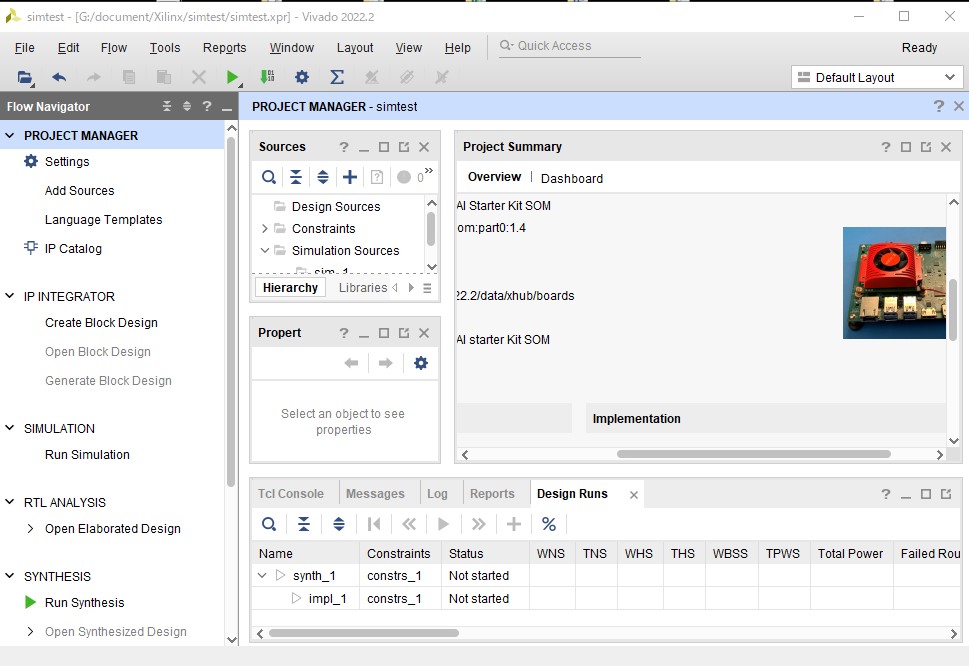

プロジェクト作成

「Vivado MLによるKria KV260のFPGAのプログラム作成(その1)」の「プロジェクト作成」に従って、プロジェクト名「simtest」のプロジェクトを作成します。

FPGA設計において、論理回路や、F/F(フリップフロップ)をハードウェア記述言語によって実現することを「RTLコーディング」と言います。

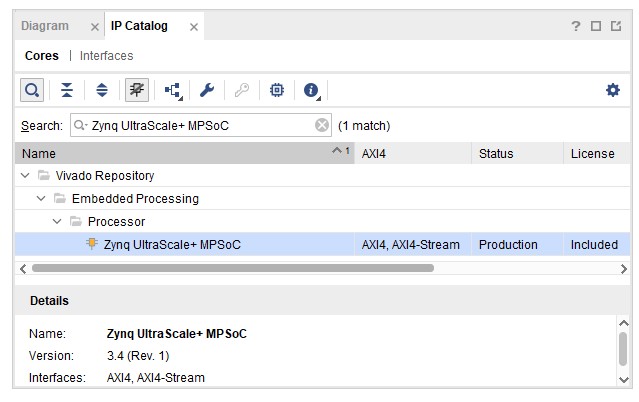

ブロックデザインの作成

「Vivado MLによるKria KV260のFPGAのプログラム作成(その1)」の「ブロックデザイン」1,2,3に従って、ブロックデザインを行い、「IP Catalog」から「Zynq UltraScale+ MPSoC」を選択します。

基本的にはハードのみで動作させ、ソフトは使用しないのでPS*1 は不要ですが、今回はクロックとリセットのみを使用します。

*1:ZYNQはPL部とPS部に分かれており, PL(Programmable Logic)部はFPGA,PS(Processing System)部はARMのCPUコアです。

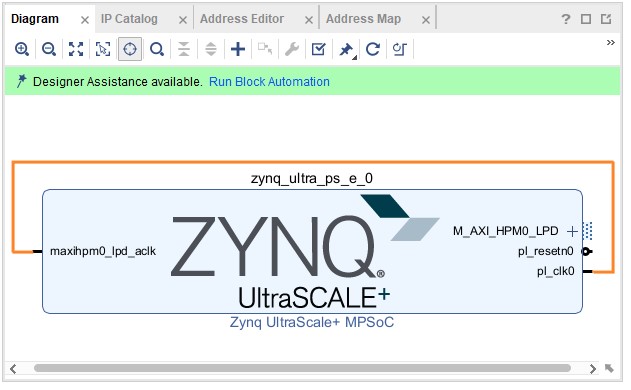

空き端子があると正常に動作しないため、pl_clk0出力をmaxihpm0_lpd_ack入力に接続し、次のようなブロック図にします。

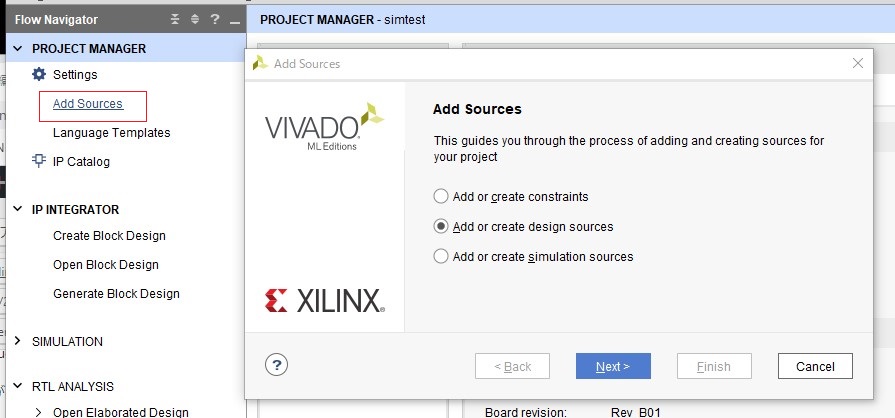

- 左端の「Flow Navigator」より「PROJECT MANAGER」の「Add Sources」をクリックし、表示したダイアログで「Add or create design sources」をチェックして「Next」ボタンをクリックします。

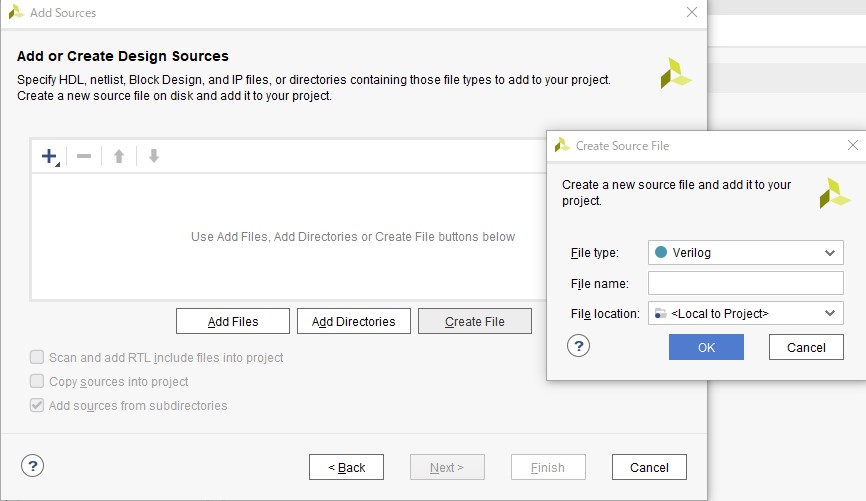

- 表示されたダイアログで、「Create File」ボタンをクリックし、表示されたダイアログでファイル名「blink」を設定して「OK」ボタンをクリックします。

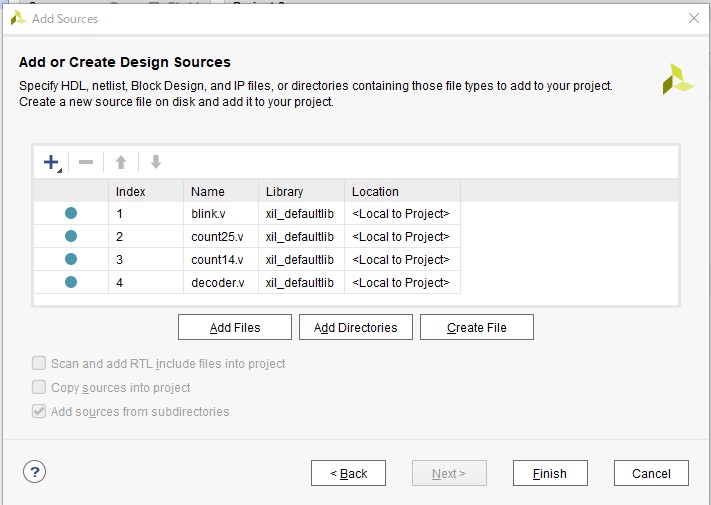

- 以降、順次ファイル名「count25」「count14」「decoder」を作成して、「Finish」ボタンをクリックします。

- 「Define Modules」ダイアログが表示されるので「ok」ボタンをクリックします。

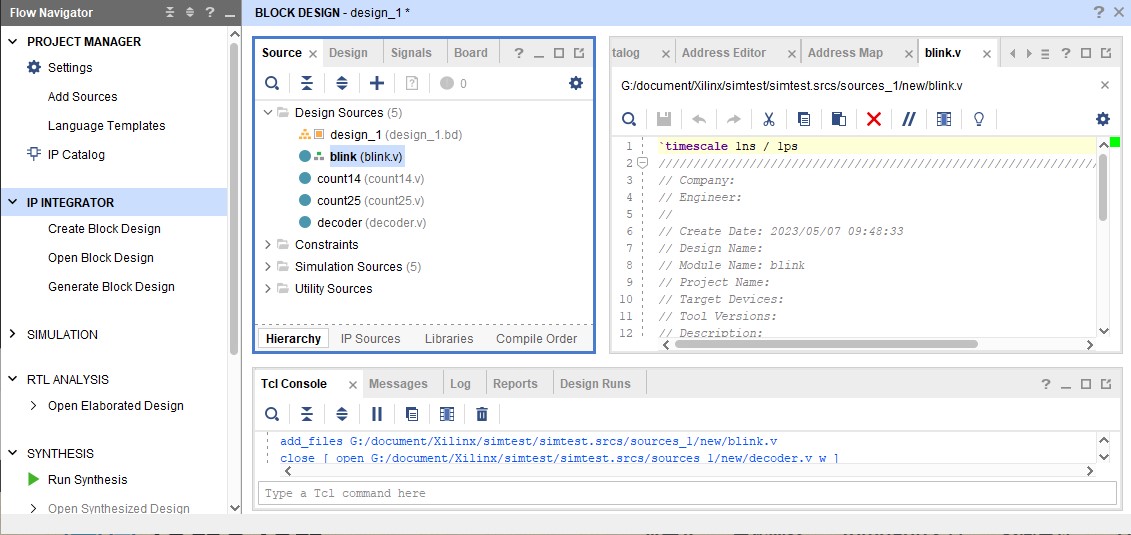

- 「Sourcer」タブをクリックし、「Design Sources」の「blink」をクリックします。

- 右側に空の「blink」のテンプレートが表示されるので、次のコードを設定してて保存します。以降対応するファイルに順次コードを保存します。

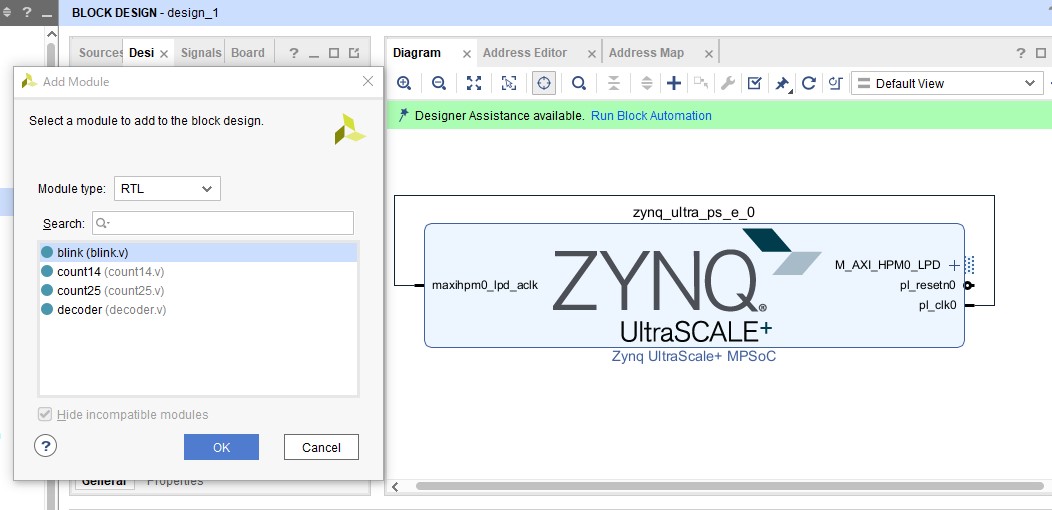

- 「Diagram」画面の 何もないところで右クリックし、表示されたメニューの「Add Module」をクリックし、表示されたモジュール選択画面で「blink」を選択し、「OK」ボタンをクリックします。

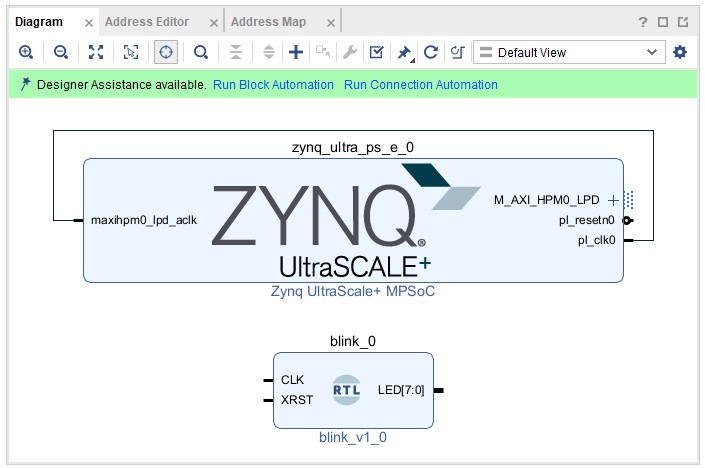

- blinkモジュールがblink_0としてインスタンスされます。

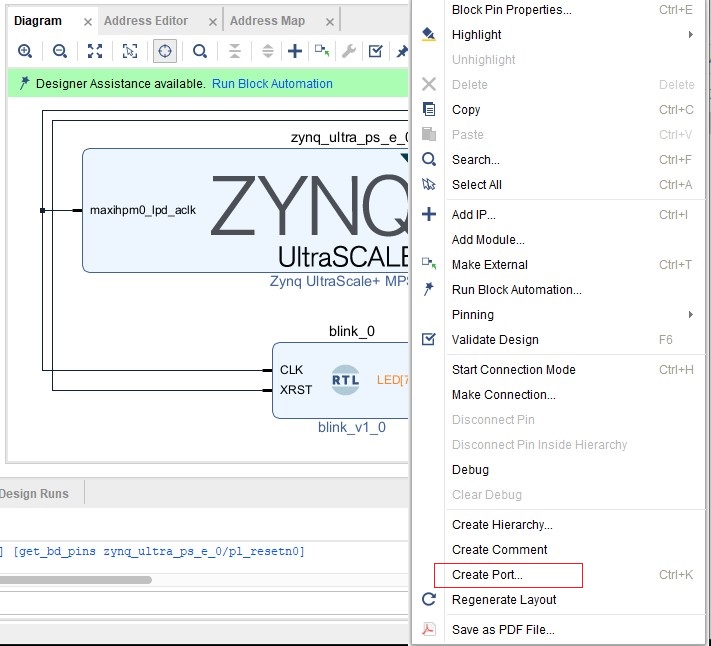

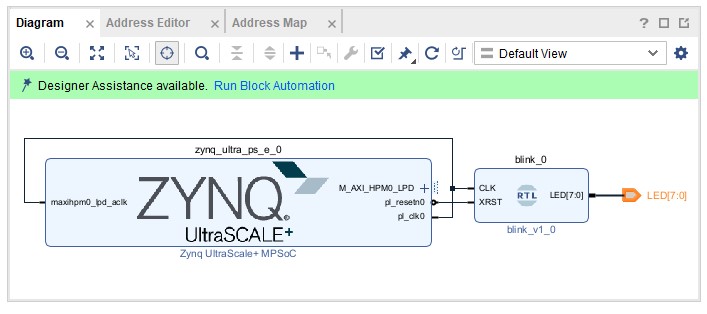

- blinkモジュールのCLK入力をZynqのpl_clk0出力に接続し、XRST入力をpl_resetn0出力に接続します。LED出力ピンを右クリックし、表示したメニューから「Create Port」を選択します。

- 「Diagram」画面の 何もないところで右クリックし、表示された「Regenerate Layout」を選択します。作成したDiagramが整形されます。

blink.v

// // LED blinking // module blink ( input CLK, input XRST, output [7:0] LED ); wire CE; wire [3:0] C14; count25 count25( .CLK(CLK), .XRST(XRST), .CE(CE) ); count14 count14( .CLK(CLK), .XRST(XRST), .CE(CE), .C14(C14) ); decoder decoder( .C14(C14), .LED(LED) ); endmodule

count25.v

/* system clock division */ module count25 ( input CLK, input XRST, output CE ); reg TEST; reg [24:0] LD; reg [24:0] count25; always @(posedge CLK) begin if (TEST) count25 = LD; if (~XRST) count25 = 25'h0; else count25 = count25 + 1'h1; end assign CE = (count25 == 25'h1ffffff); endmodule

count14.v

/* 14 advance counter for LED */ module count14 ( input CLK, input XRST, input CE, output [3:0] C14 ); reg [3:0] count14; always @(posedge CLK) begin if (~XRST) count14 <= 14'h0; else if (CE) if (count14 == 13) count14 <= 0; else count14 <= count14 + 1'h1; end assign C14 = count14; endmodule

decoder.v

/* LED Decoder */ module decoder ( input [3:0] C14, output reg [7:0] LED ); always @* begin case (C14) 0: LED = 8'b00000001; 1: LED = 8'b00000010; 2: LED = 8'b00000100; 3: LED = 8'b00001000; 4: LED = 8'b00010000; 5: LED = 8'b00100000; 6: LED = 8'b01000000; 7: LED = 8'b10000000; 8: LED = 8'b01000000; 9: LED = 8'b00100000; 10: LED = 8'b00010000; 11: LED = 8'b00001000; 12: LED = 8'b00000100; 13: LED = 8'b00000010; endcase end endmodule